# Designs for Ultra-Tiny, Special-Purpose Nanoelectronic Circuits

Shamik Das, *Member, IEEE*, Alexander J. Gates, Hassen A. Abdu, *Student Member, IEEE*, Garrett S. Rose, *Member, IEEE*, Carl A. Picconatto, and James C. Ellenbogen, *Member, IEEE*

Abstract-Designs and simulation results are given for two small, special-purpose nanoelectronic circuits. The area of special-purpose nanoelectronics has not been given much consideration previously, though much effort has been devoted to the development of general-purpose nanoelectronic systems, i.e., nanocomputers. This paper demonstrates via simulation that the nanodevices and nanofabrication techniques developed recently for general-purpose nanocomputers also might be applied with substantial benefit to implement less complex nanocircuits targeted at specific applications. Nanocircuits considered here are a digital controller for the leg motion on an autonomous millimeter-scale robot and an analog nanocircuit for amplification of signals in a tiny optoelectronic sensor or receiver. Simulations of both nanocircuit designs show significant improvement over microelectronic designs in metrics such as footprint area and power consumption. These improvements are obtained from designs employing nanodevices and nanofabrication techniques that already have been demonstrated experimentally. Thus, the results presented here suggest that such improvements might be realized in the near term for important, special-purpose applications.

*Index Terms*—Design methodology, nanocircuit, nanocomputing, nano-electronics, nanotechnology, simulation.

### I. INTRODUCTION

HE great progress toward building electronic circuits integrated on the nanometer scale [1]–[42] has opened the possibility for shrinking drastically the size and power consumption of large-scale, general-purpose electronic memories and processors. These recent advances in nanofabrication and nanoelectronics could have conspicuous, pervasive impacts for generalpurpose computing in several years' time. However, these advances also make it possible to shrink the form factor and power requirements for a wide class of much simpler circuits. Such circuits often are dedicated to specialized applications in the control and monitoring of other systems. They are less conspicuous than the larger general-purpose processors and memories, but even more pervasive. Moreover, the simplicity of these special-purpose nanocircuits is such that they might be realized industrially in only a few years, and they might find great use immediately thereafter in shrinking the larger systems in which they are em-

Manuscript received February 18, 2007; revised July 4, 2007. This work was supported by the MITRE Technology Program. This paper was recommended by Guest Editor C. Lau.

Digital Object Identifier 10.1109/TCSI.2007.907864

bedded. Thus, it is the design of these simple, special-purpose nanoelectronic circuits that we begin to consider here.

Special-purpose nanoelectronic circuits might be employed in a number of applications. For example, one class of these applications is control processing. Nanocircuits for digital control might be used to miniaturize existing applications or enable new ones, such as autonomous microsensors ("smart dust") [43], medical microrobotics [44]–[46], or other micro/nano electromechanical systems. Another class of applications that might benefit from special-purpose nanoelectronics is communications. For example, novel, tiny optical or radio data transceivers might be implemented using analog or mixed-signal nanoelectronic circuits. Also, field-programmable nanocircuits could be utilized to implement or store codecs for a compact, flexible software-defined radio system [47], [48]. Finally, as an example bridging these two classes, radio-frequency identification (RFID) systems [49] might be miniaturized or augmented using nanoelectronic information storage, control, or communications.

To begin to explore the utility of special-purpose nanoelectronic circuits for applications such as these, the authors have designed and simulated two such circuits for use in two example applications. The first circuit we consider is for digital control of a six-legged, millimeter-scale robot. This nanocircuit is derived from architectures proposed for large-scale nanoprocessors [27], [51]. As presently designed, this special-purpose nanocircuit will coordinate the motion of the legs of the robot. However, the circuit design is adaptable or extensible to control other functions on the robot.

The second nanocircuit design considered here is for an analog nanoelectronic amplifier for use in an optoelectronic communications system. This circuit could be used to implement very-wide-bandwidth optical communications. It also could be embedded in the individual pixels of an optical sensor array, enabling "smart pixel" capabilities [52].

The development of ultra-tiny, ultra-dense circuits such as these will entail overcoming significant challenges. Many of these challenges are inherited from the more complex problem of developing extended, general-purpose nanoelectronic systems. The advanced techniques that have been devised to address those larger challenges likely will be even more effective in overcoming the lower hurdles presented by simpler, special-purpose nanoelectronic circuits. Section II discusses the techniques and devices that have been selected for the designs presented here.

Following this discussion, Sections III and IV detail the design and the likely performance of the specific special-purpose digital and analog nanocircuits mentioned above. Section V provides our conclusions based upon these design efforts.

S. Das, A. J. Gates, H. A. Abdu, C. A. Picconatto, and J. C. Ellenbogen are with the Nanosystems Group at The MITRE Corporation, McLean, VA 22102 USA (e-mail: sdas@mitre.org).

G. Rose is with the Nanosystems Group at The MITRE Corporation, McLean, VA 22102, USA, and also with Polytechnic University, Brooklyn, NY 11201 USA.

# II. NANODEVICES AND NANOFABRICATION FOR SPECIAL-PURPOSE NANOELECTRONIC CIRCUITS

A number of novel nanoelectronic devices have been developed in the pursuit of extended nanocomputer systems. Such nanodevices exhibit a wide variety of electronic behaviors. These include classical behaviors such as Ohmic resistance at low voltage [8] and rectification [53]–[55]. Less common behaviors also have been demonstrated, such as negative differential resistance [13], Coulomb blockade [56], and hysteretic switching [54].

Furthermore, devices such as nanotransistors [10], [11], [14], [57] and molecular switches [5]–[8], [12], [58] have been incorporated into prototypes of small circuits, such as individual logic gates, as well as extended systems. In particular, effective use of such devices has been demonstrated in prototypes of extended nanomemory systems integrated on the molecular scale [34], [38], [40], [41]. As a result, methods now exist for fabricating systems composed of hundreds of thousands of nanodevices. Successful refinement of these methods should permit the fabrication of systems containing the many billions of devices that will be required in a nanocomputer system. In the interim, the fabrication of smaller, simpler circuits consisting of only tens or hundreds of devices should be feasible.

In addition to the demonstrated prototype systems cited above, a large number of proposals have been put forth for system architectures that would integrate one or more of the various molecular-scale devices demonstrated to date [24], [27], [28], [30]–[33], [35]–[37], [39]. All of these proposals and demonstrations are based upon a nanoelectronic system architecture termed the crossbar array [25], [29], which calls for the homogeneous distribution of nanodevices within tiled arrays of crossed nanowires.

The primary reason for making this design decision is that the fabrication of arbitrary, heterogeneous extended structures at the nanoscale remains a significant unsolved problem [59]. At larger length scales with lower densities, this capability is taken for granted, because at such scales, optical lithography is capable of precise patterning. At the molecular scale, of the several methods of integration that have been devised, the majority produce homogeneous nanowire crossbar arrays [60]–[64].

Just using such simple crossbar structures, however, it should be feasible to develop small, special-purpose nanoelectronic circuits. Thus, the circuits presented in the following sections are suitable for nanofabrication using established methods, such as nanoimprinting, and using demonstrated nanodevices, such as semiconducting nanowire transistors. The circuits also are sufficiently simple to avoid many of the challenges [59] faced in the development of extended nanoelectronic systems. The following sections of this paper will elucidate how nanocircuits simple enough to ease fabrication also can be sufficiently complex to carry out useful functions.

III. DESIGN AND ANALYSIS OF A SPECIAL-PURPOSE

DIGITAL NANOCIRCUIT: CONTROL NANOCIRCUIT FOR A

MILLIMETER-SCALE AUTONOMOUS ROBOT

### A. Overview

Using the nanowire-based structures discussed in the previous section, we consider here the design of a portion of a dig-

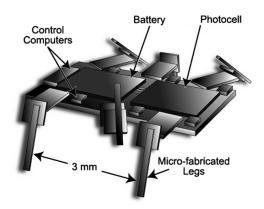

Fig. 1. Design for a millirobot as originally conceived by Routenberg and Ellenbogen [50]. The control circuit described in this article is designed to coordinate the leg movements on tiny robots such as this insect-like walking robot.

ital control processor for an autonomous, walking, millimeterscale robot. Such a "millirobot" would be the size of a small insect, and is an archetype for many other small systems that would incorporate actuation, sensing, and control. In addition, it could be employed as part of a swarm of millirobots for distributed computing and sensing.

An understanding of the overall system design options for millirobots would provide useful guidance for the selection and design of the necessary nanocircuits. Presently, there are several different designs for millimeter-scale walking robots, including a version that already has been constructed by researchers at the University of California at Berkeley [65], [66]. All of these designs have utilized off-robot power sources and control circuits, or they have dragged these necessary components behind the main body, greatly decreasing the mobility and efficiency of the tiny robot. However, the design of a millirobot with self-contained power and control systems has been proposed by Routenberg and Ellenbogen [50].

According to their design, silicon microelectromechanical systems (MEMS) technology will be utilized to constitute the millirobot. Thus, the body of this robot will be housed on a silicon die. As depicted in Fig. 1, six legs will unfold from the robot. Each will have two degrees of freedom. Prototype components such as these legs have been developed, and efforts are underway to prototype the complete mechanical subsystem [67].

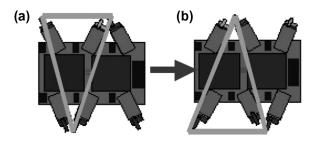

Walking will be accomplished using the tripod gait [68], [69] employed by insects that are the same size as that projected for the millirobot. The tripod gait requires the six legs of the robot to be split into two groups or tripods. Each tripod includes the two end legs on one side and the center leg on the opposite side, as represented in Fig. 2. To walk forward, the robot lifts one tripod and moves it forward while pushing the other tripod backwards until its legs reach their rearmost position. It is this motion of the twin tripods that must be generated and modulated by a control circuit.

The design of such a control circuit is governed by three main constraints. First, the master control circuit and the circuits for all six legs must occupy an insubstantial portion of the total surface area of the robot. For this application domain, the available surface area is on the order of 10 mm<sup>2</sup>. Second, the outputs

Fig. 2. The operation of the millirobot segregates the legs into two "tripods." The forward and reverse motion of the legs is depicted as the millirobot takes a half step from (a) to (b). Specifically, the triangles indicate the tripod that is to be lifted and moved forward.

of the control circuit must be suitable to drive the MEMS actuators that couple to the individual legs of the robot. Finally, because a self-contained millirobot can carry only very small energy sources, the control subsystem must be designed to consume as little power as possible.

Due to these constraints, a circuit composed of nanoelectronic devices and integrated on the nanometer scale would appear to be especially suitable. Sections III-B and III-C describe the design and simulation of a simplified version of such a nanoelectronic control circuit.

### B. Design of the Nanoscale Control Circuit

In general, a nanoelectronic circuit that implements specialpurpose functions can be designed as follows. First, an appropriate architecture must be selected. Essentially all architectures proposed thus far for nanoelectronics implement programmable circuit styles such as field-programmable gate arrays [42], [70], programmable logic arrays (PLAs) [27], or other reconfigurable fabrics [31]. These architectures specify how nanotransistors or other gain-producing nanodevices can be interconnected using post-fabrication methods such as the programming of molecular switches. As is illustrated below in Section III-C, the priorities assigned to metrics such as power consumption and system size can be used to guide the selection of a specific nanoelectronic architecture.

Once an architecture is selected, a special-purpose nanoelectronic circuit can be implemented by designing a logic network for that circuit using the nanoelectronic components available in that architecture. For example, in the CMOL architecture [70], the desired circuit would be implemented with NOR gates, whereas in the DeHon–Wilson architecture [27], the circuit would be implemented in sum-of-products form. Both of these architectures permit the implementation of arbitrary logic. However, if greater control over the device-level implementation is required, other architectures, such as the complementary symmetry array [31], could be used. This architecture provides more flexibility in the transistor-level interconnection of the circuit, as might be required for some digital logic styles, as well as most analog circuits.

The final design step is the mapping of the desired logic circuit into the chosen architectural fabric. Given the relatively small size of the special-purpose nanocircuits considered here, this can be done by hand. However, optimization tools for this task are under development by other researchers and would be

essential for mapping more extensive nanocircuitry into programmable hardware [51], [71], [72].

In the present example, a digital control nanocircuit for a millirobot, the choice of circuit style is motivated by the constraints described in Section III-A, as well as other system design issues. For example, the system design of the millirobot under consideration requires that the control circuits drive MEMS actuators. For any of the legs of the millirobot to move, the electrostatic comb drive motors that provide the mechanical power for each of the legs must resonate at a specific frequency (typically in the low kilohertz range). In particular, the control circuit outputs should be square waves at that frequency. Additionally, because the millirobot designers plan for two electrostatic actuators in a drive train arrangement for each tripod, the control signal to each leg must be composed of two individual square waves that are exactly 90 degrees out of phase. Each leg of a tripod set may be controlled with the same signal, since the three legs move in unison. However, because the motion of the opposing tripod is exactly opposite, a second pair of square waves, the inverse of the first pair, also must be generated.

These control signals could be generated by either an all-digital nanoelectronic circuit or a mixed-signal nanoelectronic circuit. Of these options, an all-digital design is desirable for two reasons. First, the fabrication of a prototype based upon this design would be eased if the design were all digital rather than mixed-signal. Mixed-signal design implies a degree of structural heterogeneity that is not required for a purely digital design. Second, a complete, practical design would need to provide many capabilities, such as high-level programmability and the ability to respond intelligently to environmental data sensed by the robot. These capabilities are implemented most easily using digital logic. Although the design presented here is a simplified version intended as a proof of principle, it also is intended to be scalable to a complete design. Thus, the design presented here is a digital implementation.

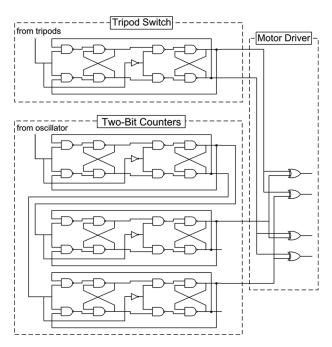

Fig. 3 gives a schematic diagram of a simple all-digital circuit that produces the desired control signals. This design is split into three major components: two-bit counters, tripod switch, and motor driver.

These components are driven by a clock signal generated by an oscillator. This oscillator drives the circuit at four times the desired resonant frequency. The oscillator could be implemented as a conventional electronic circuit. Alternatively, new, smaller nano-electromechnical system (NEMS) oscillators presently under development may provide a smaller replacement for these conventional oscillators [73]. As a third option, ultra-tiny nanoelectronic oscillator circuits could be designed to provide the required signals [74].

The output of the oscillator is fed into two divide-by-four circuits (i.e., two-bit counters) that are used to generate quadrature outputs at the desired frequency. The motor driver is used to multiplex the correct outputs onto the actuators. The "tripod switch," which controls the motor driver, obtains feedback from the legs: when the forward-moving legs have reached their furthest extent, a voltage pulse is sent to the tripod switch, which indicates to the motor driver that its outputs should be inverted.

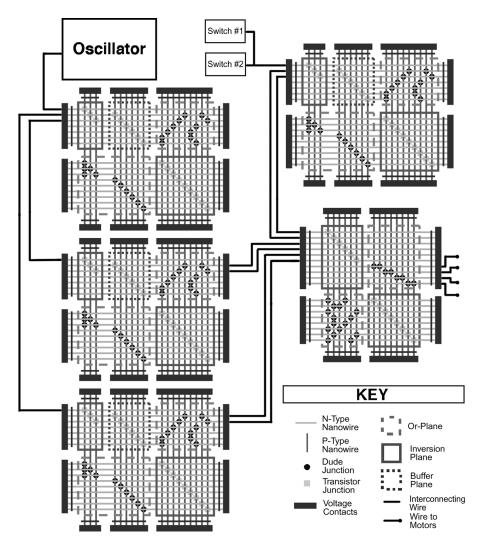

A proposed layout for a nanoelectronic circuit that implements these functions is shown in Fig. 4. For this nanoelectronic

Fig. 3. Schematic of a digital control circuit that produces a tripod gait for a millimeter-scale walking robot.

layout, the nanocomputer architecture of DeHon and Wilson [27] was adapted. This architecture specifies how nanowire transistors and diodes, such as those demonstrated by Lieber *et al.* [10], [11], [54], [57], might be employed to construct a PLA . DeHon and Wilson propose the use of extended arrays of tiled nano-PLAs [25] to constitute a computer system.

In a similar manner, it should be possible to utilize fewer, simpler PLAs to develop small, special-purpose circuits such as the nanoelectronic control circuit proposed here. Fig. 4 shows how suitable nanowires might be arranged in a set of crossbar arrays to construct a set of nano-PLAs. Field-effect transistors are specified to be placed at the nanowire junctions indicated by the boxes in the figure. The resulting PLA structure then can be programmed by the method described by DeHon and Wilson [27] in order to produce the desired control-circuit functionality. The functionality required for this example is provided by programming into the "on" state the diodes marked by black dots in Fig. 4.

The use of nano-PLAs to synthesize a nanoelectronic control circuit provides several advantages. For example, the PLA-based architecture allows for the programming of control-circuit functionality post-fabrication. Thus, the techniques already established for the nanofabrication of PLA-based general-purpose nanocomputer systems also might be employed for the fabrication of the simpler, special-purpose circuits considered here. In addition, because of the small size of these circuits, established fabrication techniques [26] might be sufficient to provide immunity to the defect rates and process variations that are expected to plague larger, general-purpose nanoelectronic systems [75].

The use of nano-PLAs also introduces performance tradeoffs that must be considered in the design of the control circuit. Two logic styles have been proposed by DeHon and Wilson: static and dynamic [27]. The dynamic logic style is likely to result in implementations that consume less power since the proposed nanowire-based static logic draws significant static current. Thus, the dynamic style would seem to be more desirable for application in the millirobot. Unfortunately, dynamic voltage signals are not suitable to drive the MEMS actuators in the proposed robot. These actuators require true square waves at a fixed frequency. However, dynamic logic outputs would transition at both the desired output frequency and the input oscillator frequency. Thus, these outputs would have to be converted to static voltage signals that switch only at the desired frequency. Implementing such a dynamic-to-static logic converter would be difficult in the array-based nanowire architectures [27], [51] considered here. An additional drawback is that dynamic circuits are susceptible to current leakage because dynamic logic is based upon charge storage. In order to overcome this leakage, a dynamic implementation would need to be clocked at a much higher rate than would be required for a static implementation. This higher clock rate eliminates some power savings.

Thus, a static logic design was developed as shown in Fig. 4. In the section that follows, the simulation and analysis of this design is discussed.

#### C. Simulation and Analysis of the Nanoscale Control Circuit

In order to assess the performance of the nanoelectronic circuit given in Fig. 4, the circuit was laid out and simulated using the Cadence DFII software package [76]. Examination of the layout (provided in Fig. 4) demonstrates the millirobot control circuit to be very compact. The nanowires in this circuit are assumed to be 10-nm wide with 10-nm spacing. The microwires are assumed to be those available in a 90-nm silicon process. Based upon these assumptions, the proposed nanocircuit is only 3.6  $\mu$ m<sup>2</sup> in size. In comparison, a gate-for-gate identical circuit fabricated entirely using 90-nm standard cells [77] would measure approximately 92  $\mu$ m<sup>2</sup> in size—roughly 25 times larger. More importantly, a full microcontroller fabricated in a conventional CMOS process would occupy an area of anywhere from 2.4 to 400 mm<sup>2</sup> or more [78]. This conventional microcontroller would be too large for the millirobot considered here. However, a full nanocontroller 25 times smaller could fit easily within the desired form factor. Thus, the nanocircuit design and simulation results presented here strongly support the possibility of miniaturizing these conventional control circuits down to a size that would permit their integration into tiny robots.

Simulations of special-purpose nanocircuitry were carried out using a methodology devised originally for simulating general-purpose nanomemories and nanoprocessor systems. This methodology, plus the associated CAD environment and device models, is described in detail in previous work by the present authors [54], [59], [79]. In broad outline, four steps were involved in that approach. First, empirical data were obtained for the desired nanodevices and interconnect structures. Second, these data were encapsulated into Verilog-A models [54], [59]. Third, a system-level schematic representing Fig. 4 was assembled within the Cadence Virtuoso environment [76]. Finally, the performance of the circuit was simulated using the Cadence Spectre simulator [76].

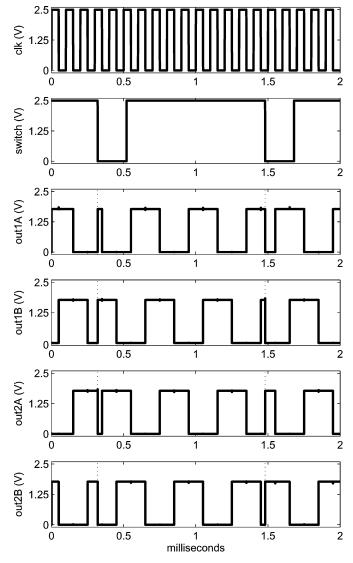

In this simulation, a frequency of 10 kHz was assumed for the input oscillator. Thus, 2.5-kHz signals were expected for each of the four outputs. The simulation was run for 2 ms (i.e., 20 cycles

Fig. 4. Layout of an entire nanowire-based nanoelectronic controller to produce a millirobot's tripod gait.

of the oscillator). During the simulation run, the tripod switch input signal was pulsed twice to confirm correct switching of the output signals.

The results of these simulations are shown in Fig. 5. These results reveal that the circuit produces the correct quadrature outputs. Specifically, output "out1B" lags output "out1A" by 90°, and outputs "out2A" and "out2B" are the inverses of outputs "out1A" and "out1B," respectively. Also, all the output signals invert properly when the tripod switch input is pulsed.

The power consumption of the nanocircuit was measured via simulation to be 1.9  $\mu$ W. This compares poorly with 156.9 nW for the implementation using 90-nm silicon standard cells [77]. Thus, in contrast with expectations, this design actually is predicted to consume 12 times as much power as an equivalent conventional circuit. It was determined that the primary reason for this unexpectedly high power consumption is the use of the static version of the DeHon–Wilson architecture. The static circuit style employed in this architecture is a "pseudocomplementary" style, in which some pulldown chains are implemented using p-type transistors. Thus, one conclusion that might be drawn from these simulation results is that if static logic is required, nanoarchitectures that em-

ploy true complementary circuit layouts might be preferable. This complementarity would reduce static power consumption greatly. An example of a nanoarchitecture that offers this circuit style is the complementary symmetry array proposed by the Hewlett-Packard Corporation [51].

Nevertheless, based on the simulation results discussed here, a nanoelectronic circuit fabricated to the design specifications given in Fig. 4 is predicted to produce signals of the shape needed for control of the millirobot. Such a circuit would be much smaller than could be achieved using conventional silicon fabrication processes. With further research, it is expected that this circuit also could be made to consume very little power.

IV. DESIGN AND ANALYSIS OF A SPECIAL-PURPOSE ANALOG NANOCIRCUIT: TRANSIMPEDANCE AMPLIFIER (TIA) FOR A NANOSCALE OPTOELECTRONIC RECEIVER

### A. Overview

In the previous section, we considered the design of a special-purpose *digital* nanocircuit. In this section, we consider an *analog* nanoelectronic circuit for use in optoelectronic applications. A key function in such applications is the ability to convert

Fig. 5. Simulated inputs and outputs of the millirobot control nanocircuit. The first two signals represent inputs from the oscillator ("clk") and leg tripods ("switch"), respectively. The remaining four signals represent the outputs of the circuit that drive one tripod ("out1A" and "out1B") and the other tripod ("out2A" and "out2B").

a small current to a large voltage. One type of common analog circuit for this purpose is a TIA. Here, we discuss how very useful circuits such as a TIA might be miniaturized significantly using nanoelectronic devices and designs.

Like digital design, analog circuit design is driven by performance. However, the performance metrics for analog design differ from those employed for digital design. Common metrics include not only gain, but also bandwidth, dynamic range, and linearity. Noise performance also factors into many analog system designs.

Unlike digital design, analog design typically is not focused on system size. Primarily, this is because relatively few individual devices are required to construct an analog system. For example, the commonly-used LM741 operational amplifier consists only of 24 transistors, 12 resistors, and 1 capacitor in the implementation by Fairchild Semiconductor [80]. The most complex analog systems might employ just a few op-amps

or other parts of similar device count. This is in contrast to complex digital systems such as modern Intel processors, which presently utilize as many as half a billion transistors [81].

However, three issues complicate this direct comparison of system size according to device count [82]. First, the individual transistors in analog applications usually are much larger than those in digital systems. Second, passive components, i.e., resistors, capacitors, and inductors, consume area that is disproportionate to their relative device counts. Third, matching (i.e., the requirement that process variations affect paired devices in equal amounts) places constraints that tend to expand system layout.

Therefore, nanoelectronic devices might have significant impacts on analog system design, despite the relatively low number of devices employed in such systems. These impacts would be realized primarily in the first two of the above issues. Specifically, nanotransistors [10], [11], [14], [57] might be employed to reduce the area consumed by active devices. Also, a number of nanoelectronic devices have been proposed for use as passives, such as molecular-scale resistors [5], [58] and carbon-nanotube-based inductors [83], [84].

Furthermore, the ultra-high density of integration available with digital nanoelectronics also might be employed for specific analog applications. For example, ultra-tiny mixed-signal sensor platforms, a.k.a. "smart dust" [43], will require nanoelectronics in order to be realized at the millimeter or sub-millimeter scale. Other applications exist in optical sensing and communications. In sensing or imaging, nanoscale devices and ultra-dense integration might be employed to develop ultra-tiny pixels or so-called "smart pixels" [52] that integrate optical sensing with electronic amplification. Similarly, in communications, nanoscale photonic devices [85]–[90] might be integrated very densely in order to produce ultra-high-band-width optical communications systems in a small form factor.

A central component of these latter applications consists of optoelectronic conversion followed by electronic amplification. Thus, the development of a nanoscale circuit that accomplishes these tasks could enable the ultra-miniaturization of a variety of systems. The following sections describe the design and analysis of such a circuit, an analog nanoelectronic amplifier that couples directly to a nanoscale photosensor. This discussion addresses first the general issues that are likely to arise in analog nanoelectronic circuit design. Then, it proceeds to the design and analysis of an example amplifier based upon presently available nanoelectronic devices [57], [58].

# B. Issues Specific to the Design of Analog Nanoelectronic Circuits

Unlike digital circuits, analog circuits exploit the continuous spectrum of behavior of their constituent devices. Specifically, digital circuits typically employ electronic devices as switches. Insofar as a nanoelectronic device approximates an ideal, discrete switch, it can be of use for digital applications. In contrast, analog circuits usually rely upon continuous, linear behavior around a nominal central voltage or current point (i.e., the operating point). The degree to which a candidate nanodevice produces continuous, linear behavior impacts the usefulness of that nanodevice for analog applications.

Thus, while a variety of devices have been proposed for use in digital nanoelectronic applications, only a subset of these devices is appropriate for analog circuits. For example, Coulomb blockade devices such as single-electron transistors [56] or quantum-dot cellular automata [91], [92] are unlikely to be suitable, due to their characteristic stair-step current-voltage behavior. On the other hand, nanotransistors [10], [11], [14], [57] are highly suitable since their behavior is essentially that of conventional transistors.

However, the behavior of presently-available nanotransistors does depart in some ways from that of conventional transistors. It is expected [11] that as development of such nanodevices matures, these present limitations will be overcome. In the interim, it is useful to consider how these limitations might affect the design and performance of analog nanoelectronic systems.

Present limitations to nanotransistor behavior occur in two areas, gain and bandwidth. Both of these limitations arise from the transistor transconductance,  $g_m$ . In presently available nanodevices, the transconductance may be orders of magnitude lower than is achievable with conventional transistors [11], [93]. This directly limits the gain that can be produced by nanoelectronic devices and small analog nanoelectronic circuits. The bandwidth of individual transistors is dictated by the transition frequency,  $f_T$ . For field-effect transistors, this is given approximately by

$$f_T = \frac{g_m}{2\pi (C_{as} + C_{ad})} \tag{1}$$

where  $C_{gs}$  and  $C_{gd}$  are the coupling capacitances from the transistor gate to the source and drain respectively [94]. In nanotransistors, the lower  $g_m$  results in a reduced transition frequency, despite the reduced  $C_{gs}$  and  $C_{gd}$ . As a result, the bandwidth of analog nanoelectronic systems is impacted adversely, as well.

In addition to limitations in nanotransistor performance, there exist challenges arising from the use of nanoscale passives. For example, due to the impedance scaling that occurs as device dimensions shrink, moderately sized resistors, e.g., less than  $1\,\mathrm{M}\Omega$ , would be difficult to fabricate using known nanodevices or nanoscale interconnects. Similarly, large capacitances, e.g., more than 1 fF, also would be difficult to obtain without undermining the intent to ultra-miniaturize. For these reasons, nanocircuit frequency compensation is made difficult, since the primary methods of compensating integrated circuits involve the use of resistors and capacitors with specifically tailored values.

Beyond the performance of the active and passive devices that constitute analog circuits, the impact of parasitic elements also presents a challenge for analog nanoelectronic circuit design. For example, the parasitic resistance of interconnects is affected adversely by the shrinking of the wire cross-sectional areas. Thus, as is the case with state-of-the-art microelectronic analog design, the first-pass design of analog nanoelectronic circuits also must consider parasitic elements together with the intended devices.

Finally, as indicated in Section II, it will be difficult to fabricate arbitrary circuit topologies at the nanometer scale. Instead, nanoelectronic circuits must be designed so that they

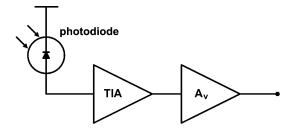

Fig. 6. Architecture for an optoelectronic sensing system. The photodiode converts an incoming optical signal into an electric current. This current is converted to voltage by an TIA. This voltage is amplified further by the amount  $A_v$ , as may be needed for subsequent signal processing.

leverage the relative ease of fabrication of regular structures such as crossbar arrays.

Notwithstanding the significant challenges that are enumerated here, the available design space still permits the development of analog nanocircuits for important applications in the near term. The design of one example circuit, a nanoscale analog amplifier, is discussed in detail in the next section.

### C. Design of a Nanoscale TIA

Integrated analog amplifier circuits play a key role in optoelectronic sensing and communications systems. A typical architecture for such systems is shown in Fig. 6. In this architecture, an optical sensor, e.g., a photodiode, produces an electric current in response to an incoming optical signal. Amplifiers are used first to convert the photoelectric current into a voltage and then to increase the strength of that voltage signal.

Recent developments in nanophotonics indicate that ultraminiaturization of such an optical system might be feasible. For example, quantum-dot-based [85], [95] and nanowire-based [86]–[90] optoelectronics have been demonstrated. In particular, some of these nanowire-based approaches [88] utilize the same semiconductors that have been employed as the gate electrodes of nanowire transistors [9]. Thus, if a current-to-voltage converter could be synthesized using these nanowire transistors, it could be coupled very closely to a nanophotonic sensor. Such close coupling might result in improved performance and very small size for the overall system.

Typically, an TIA is used as the current-to-voltage converter. The goal of a TIA is to produce high transimpedance with a relatively low input impedance [96]. The transimpedance determines system sensitivity, while the input impedance usually dictates the receiver bandwidth. Thus, TIA circuits can be useful for high-bandwidth, high-sensitivity applications.

It is common to implement a TIA using an inverter with resistive feedback [97]. Thus, any approach for fabricating digital inverter nanocircuits conceivably could be adapted to implement a TIA. One promising approach is the complementary symmetry array proposed by the Hewlett-Packard Corp. [31] for nanocomputer systems. This approach combines both p-type and n-type nanoscale FETs with metal nanowire interconnects. Also, the underlying use of arrays of crossed nanowires would permit the implementation of the feedback loop that will be needed for a TIA.

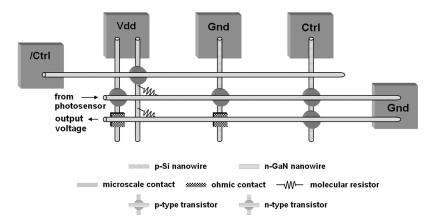

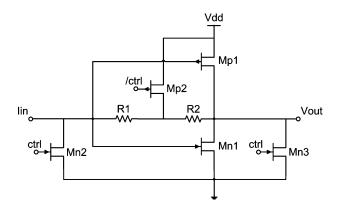

Based on the complementary symmetry array approach, a layout for a nanoscale TIA was developed and is shown in Fig. 7.

Fig. 7. Layout of a nanoscale TIA composed of nanowires, nanoscale transistors, and molecular resistors.

Fig. 8. Schematic of a nanoscale TIA.

The corresponding circuit schematic is given in Fig. 8. This layout uses two crossed-nanowire transistors ( $M_{n1}$  and  $M_{p1}$  in Fig. 8) to form a CMOS-like inverter. These nanowires are chosen to be semiconductors as appropriate to devise p-type or n-type transistors, as well as other active nanodevices. In particular, the gate for the transistors could be a gallium nitride nanowire that also could serve as part of a nanoscale photodiode. Aside from the sites required for active devices, these nanowires are intended to be metallized (e.g., silicided), in order to reduce parasitic resistance. The nanowires are taken to be 10 nm in diameter. Connected to these nanowires are microwire contacts taken to be minimum-size metallization features from 65-nm CMOS.

Two tunable molecular resistors [58] are employed in series as the feedback resistor. Because their resistance is tuned by an applied voltage, it is necessary to have electrical access to these resistors from the microscale. One way to achieve this would be to attach additional microwire contacts. However, this would introduce large capacitances into the circuit. Instead, three additional nanotransistors  $(M_{\rm n2}, M_{\rm n3}, {\rm and}\ M_{\rm p2}\ {\rm in}\ {\rm Fig.}\ 8)$  are used to connect the resistors to the microwire contacts.

The performance of this TIA is optimized as follows. To first order, the transimpedance is given by

$$Z_T = \frac{A_v R_f - R_o}{1 + A_v} \tag{2}$$

where  $A_v$  is the inverter voltage gain,  $R_o$  is the inverter output resistance, and  $R_f=R_1+R_2$  is the feedback resistance. The bandwidth,  $f_{-3~{\rm dB}}$ , is given by

$$f_{-3 \text{ dB}} = \frac{1 + A_v}{2\pi (R_o + R_f)C_p}$$

(3)

where  $C_p$  is the capacitance of the photosensor. The metric of interest is the gain-bandwidth product, subject to a minimum-bandwidth constraint.

To choose a reasonable bandwidth for the TIA, the transition frequency of the nanotransistors must be determined first. Ideally, this information would be obtained from experimental measurements that characterize the high-frequency behavior of these transistors. However, such experiments have yet to be carried out. In advance of these experiments, the transition frequency can be estimated from empirical models and first principles.

Models for crossed-nanowire silicon FETs were devised in previous work [59]. Using these models and first-order approximations, values for  $g_m$ ,  $C_{gs}$ , and  $C_{gd}$  can be derived. The transition frequency then follows from (1). Specifically, a supply voltage of 5 V yields a  $g_m$  of  $3.58 \times 10^{-7}$  S. Using a parallel-plate approximation for 10-nm nanowires with 1-nm oxide thickness gives  $C_{gs} \approx 3.3$  aF and  $C_{gd} \approx 1$  aF. The resulting  $f_T$  is 13.1 GHz. To provide sufficient design headroom, 1 GHz was chosen for the desired bandwidth  $f_{-3 \text{ dB}}$ .

Given this minimum value for  $f_{-3~{\rm dB}}$ , a range of values for  $R_f$  can be determined. First, values for  $A_v$ ,  $R_o$ , and  $C_p$  must be determined.  $C_p$  is assumed to be 100 aF, a reasonable value for a nanoscale photosensor.  $R_o$  and  $A_v$  are calculated using the transistor models from previous work [59] and positing a supply voltage of 5 V. The resulting values are  $R_o=15.0~{\rm M}\Omega$  and  $A_v=10.7$ .

Given these values, the minimum-value constraint on  $R_f$  can be determined by requiring that the gain-bandwidth product (GBW) of the TIA exceed  $1/2\pi C_p$ , the GBW for a resistor used passively. Multiplying (2) and (3) yields  $R_f > 2R_o/(A_v-1)$ . Likewise, the maximum value for  $R_f$  is determined by (3). For the TIA under consideration, the resulting constraint is  $3.08~\mathrm{M}\Omega < R_f < 3.66~\mathrm{M}\Omega$ .  $R_f = 3.3~\mathrm{M}\Omega$  is chosen as the approximate midpoint of the range. A resistor of this value

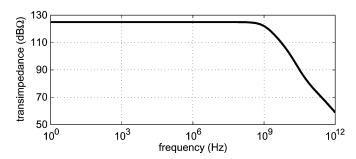

Fig. 9. Simulated transimpedance versus frequency for the proposed amplifier.

should be synthesizable from two molecular resistors of the type described by Stewart *et al.* [58], if scaled to the dimensions desired for this nanocircuit. Furthermore, this large resistance should result in low input-referred noise current.

The prospective performance of a circuit based upon this design is given in the next section.

### D. Simulation and Analysis of the Nanoscale TIA

Using the values stated above for the supply voltage, feedback resistor, photosensor capacitance, and physical dimensions, the circuit of Fig. 8 was simulated using the Cadence DFII software package [76]. The transimpedance was determined to be  $1.77M\Omega~(125.0~\text{dB}\Omega)$  and the bandwidth was 1.014~GHz. The transimpedance as a function of frequency is given in Fig. 9.

For this circuit, the total power dissipation was measured via simulation to be 1.52  $\mu$ W. This compares very favorably with 5 mW for the same circuit implemented in a conventional 65-nm process, as estimated from process data [98], [99]. However, this three-orders-of-magnitude improvement in power consumption comes with several tradeoffs. For example, conventional transistors, with  $f_T$  in the hundreds of gigahertz, are much faster than presently available nanotransistors. Thus, a TIA implemented using conventional transistors could have a much higher bandwidth. As another example, the gain-bandwidth product of a TIA implemented using conventional transistors also would be higher than that of the TIA nanocircuit described here.

The simulated nanocircuit also outperforms the conventional TIA circuit in noise. In this nanocircuit, the primary sources of noise are thermal noise from the feedback resistor and from the transistor channels. Due to the lower transconductance of the nanotransistors, the channel noise in these transistors is much less than that of the conventional transistors. However, the larger output resistance in the nanocircuit means that more of this noise current is referred to the input. Fortunately, the overall impact is a lower input-referred noise current:  $92 \text{ fA}/\sqrt{\text{Hz}}$  for the nanocircuit versus  $201 \text{ fA}/\sqrt{\text{Hz}}$  for the conventional TIA. Over the entire bandwidth, this amounts to 3.66 nA for the nanocircuit versus 10.9 nA for the conventional TIA.

Finally, the layout of this TIA nanocircuit occupies an area of  $0.65~\mu m \times 0.22~\mu m$ , or  $0.143~\mu m^2$ . In contrast, a TIA fabricated in a 65-nm CMOS process would occupy an area of at least  $100\mu m^2$ , and as much as  $0.1~mm^2$ , depending on the process by which the feedback resistor is fabricated. Thus, the nanocircuit presented here offers several orders of magnitude improvement in area.

#### E. Discussion

From these simulation results, several points merit further discussion. First, the design of practical analog nanoelectronic circuits is possible, despite the large output resistance of presently available nanoelectronic transistors. This large  $R_o$ , in the tens of M $\Omega$ , necessitates a departure from traditional design methodology. For example, it can be seen from (2) and (3) that in conventional inverter-based TIAs, the transimpedance and bandwidth are controlled largely by the feedback resistance. Also, the gain-bandwidth product of a conventional inverter-based TIA necessarily will exceed that of a passive resistor TIA, so long as the transistors' output resistance is relatively low. In contrast, the design parameters of the nanoelectronic TIA must be selected carefully in order to outperform a nanoelectronic resistor.

Second, the noise performance of analog nanocircuits such as this one appears to be competitive with state-of-the-art microelectronic circuits. However, some important factors must be considered further if a design such as this is to be implemented. Primarily, the noise analysis presented here considers only basic data that are available at this stage of nanodevice development. It is likely, for example, that novel nanodevices such as the tunable molecular resistor [58] will contribute excess noise due to stochastic aspects of their functionality. Devices such as these are not yet well understood, and more extensive characterization must be carried out before they can be used in robust circuits and systems.

Third, the simulation results indicate that due to the low drive current and correspondingly large output resistance of the nanotransistors, high transimpedance is achieved more easily than high bandwidth. Thus, nanocircuits such as the one presented here should be considered primarily for applications where high sensitivity is required. Fortunately, the applications suggested in this paper, e.g., optical receivers for ultra-tiny "smart" pixels, meet this requirement.

In particular, the prospective size and power performance of the nanocircuit presented here make it (or a variant thereof) a highly suitable candidate for use in such a pixel. In contrast to conventional CMOS TIA circuits, which are too large, this nanocircuit readily could be incorporated into pixels of area  $25\mu\text{m}^2$  or less, as are found in state-of-the-art active pixel (CMOS) sensors [100]. Further, in conventional CMOS pixels, as much as 75% of the pixel area is consumed by the electronic amplifier circuitry [101]. The detector fill factor in these pixels would be improved significantly by the use of ultra-tiny nanoelectronic circuits such as this one.

Thus, despite the challenges inherent to the use of novel nanoelectronic devices, plus the changes in time-tested methodology such challenges would require, it is clear that nanoelectronic circuits may provide important benefits in the design of analog systems.

### V. SUMMARY AND CONCLUSIONS

The pursuit of general-purpose nanocomputer systems integrated on the molecular scale has led to significant progress in the development of both novel nanoelectronic devices and inventive techniques for the nanofabrication of extended systems. The results detailed in this paper demonstrate that these same

devices and techniques also might be applied to an application space that is relatively unexplored for nanoelectronics, that of smaller, special-purpose nanoelectronic circuits. Furthermore, these results indicate that substantial benefits might be obtained for applications if such nanocircuits can be utilized.

To illustrate these points, two example nanocircuits have been examined above, one digital and one analog. The digital circuit, a control nanocircuit for an autonomous millirobot, would be an enabling technology for such a robot. The design and simulations considered here demonstrate that with presently available nanotechnologies, the necessary control circuitry could be made to fit within the desired form factor for the robot. Thus, it is likely that a nanoelectronic circuit designed using the principles described here could be useful in addressing the broader issue of further miniaturizing micromachine systems. Utilizing nanocircuitry such as that described here, it is hoped that such circuitmachine systems might integrate both the control circuit and the MEMS mechanisms in one very small package. These very much smaller, "smart" mechanisms could have many potential applications wherever MEMS devices presently are being investigated for use: from communication networks, to biomedical therapeutics, to the millirobot addressed in this research.

Likewise, the analog nanocircuit described in this paper, a TIA for an optoelectronic sensor or receiver, could enable high bandwidth optical communications in a very small form factor. Designs such as the one presented for this amplifier also could enable "smart pixel" sensor arrays to be realized. The analysis presented for this amplifier demonstrates that analog nanoelectronics can provide more complex functionality for such a sensor system, while simultaneously increasing the area available for optical detection.

Example nanocircuits such as these provide strong motivation for further investigation and development of application-specific, special-purpose nanoelectronic circuits and systems. The designs and simulations presented in this paper bear out in detail the premise that via the use of nanoelectronics, substantial improvements in size and power may be obtained over existing systems. Further, new applications may be enabled by the development of such nanocircuits. Thus, significant opportunities exist in the near future for fabrication and prototyping experiments to realize these benefits for important applications.

## ACKNOWLEDGMENT

The authors thank Prof. A. DeHon of the University of Pennsylvania, Prof. J. Heath of the California Institute of Technology, Prof. C. Lieber of Harvard University, plus R. S. Williams, P. Kuekes, D. Stewart, and G. Snider of the Hewlett-Packard Corporation for their many generous discussions and for providing information regarding their nanoscale devices and system designs.

### REFERENCES

- A. Bachtold, P. Hadley, T. Nakanishi, and C. Dekker, "Logic circuits with carbon nanotube transistors," *Sci*, vol. 294, no. 5545, pp. 1317–1320, Nov. 9, 2001.

- [2] C. P. Husband, S. M. Husband, J. S. Daniels, and J. M. Tour, "Logic and memory with nanocell circuits," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1865–1875, Sep. 2003.

- [3] R. K. Kummamuru, J. Timler, G. Toth, C. S. Lent, R. Ramasubramaniam, A. O. Orlov, G. H. Bernstein, and G. L. Snider, "Power gain in a quantum-dot cellular automata latch," *Appl. Phys. Lett.*, vol. 81, no. 7, pp. 1332–1334, Aug. 12, 2002.

- [4] C. P. Collier, E. W. Wong, M. Belohradsky, F. M. Raymo, J. F. Stoddart, P. J. Kuekes, R. S. Williams, and J. R. Heath, "Electronically configurable molecular-based logic gates," *Sci*, vol. 285, no. 5426, pp. 391–394, Jul. 1999.

- [5] C. P. Collier, G. Mattersteig, E. W. Wong, Y. Luo, K. Beverly, J. Sampaio, F. M. Raymo, J. F. Stoddart, and J. R. Heath, "A [2]catenane-based solid state electronically reconfigurable switch," *Sci*, vol. 289, pp. 1172–1175, 2000.

- [6] Y. Luo, C. P. Collier, J. O. Jeppesen, K. A. Nielson, E. Delonno, G. Ho, J. Perkins, H. Tseng, T. Yamamoto, J. F. Stoddart, and J. R. Heath, "Two-Dimensional molecular electronics circuits," *ChemPhysChem*, vol. 3, no. 6, pp. 519–525, Jun. 17, 2002.

- [7] Y. Chen, D. A. A. Ohlberg, X. Li, D. R. Stewart, J. O. Jeppesen, K. A. Nielsen, J. F. Stoddart, D. L. Olynick, and E. Anderson, "Nanoscale molecular-switch devices fabricated by imprint lithography," *Appl. Phys. Lett.*, vol. 82, no. 10, pp. 1610–1612, Mar. 2003.

- [8] Y. Chen, G. Y. Jung, D. A. A. Ohlberg, X. M. Li, D. R. Stewart, J. O. Jeppesen, K. A. Nielsen, J. F. Stoddart, and R. S. Williams, "Nanoscale molecular-switch crossbar circuits," *Nanotechnology*, vol. 14, pp. 462–468, 2003.

- [9] Y. Huang, X. F. Duan, Y. Cui, L. J. Lauhon, K. H. Kim, and C. M. Lieber, "Logic gates and computation from assembled nanowire building blocks," *Sci.*, vol. 294, no. 5545, pp. 1313–1317, 2001.

- [10] A. B. Greytak, L. J. Lauhon, M. S. Gudiksen, and C. M. Lieber, "Growth and transport properties of complementary germanium nanowire field-effect transistors," *Appl. Phys. Lett.*, vol. 84, no. 21, pp. 4176–4178, May 2004.

- [11] Y. Cui, Z. Zhong, D. Wang, W. U. Wang, and C. M. Lieber, "High performance silicon nanowire field effect transistors," *Nano Lett.*, vol. 3, pp. 149–152, 2003.

- [12] P. J. Kuekes, D. R. Stewart, and R. S. Williams, "The crossbar latch: Logic value storage, restoration, and inversion in crossbar circuits," *J. Appl. Phys.*, vol. 97, pp. 034 301-1–034 301-5, 2005.

- [13] J. Chen, M. A. Reed, A. M. Rawlett, and J. M. Tour, "Large on-off ratio and negative differential resistance in a molecular electronic device," *Sci*, vol. 286, pp. 1550–1552, 1999.

- [14] S. J. Tans, A. Verschueren, and C. Dekker, "Room-temperature transistor based on a single carbon nanotube," *Nature*, vol. 393, no. 6680, pp. 49–52, May 1998.

- [15] S. J. Wind, J. Appenzeller, R. Martel, V. Derycke, and P. Avouris, "Vertical scaling of carbon nanotube field-effect transistors using top gate electrodes," *Appl. Phys. Lett.*, vol. 80, no. 20, pp. 3817–3819, May 20, 2002

- [16] G. Stix, "Nanotubes in the clean room," Sci. Amer., pp. 82–85, Feb. 2005.

- [17] A. Javey et al., "High performance n-type carbon nanotube field-effect transistors with chemically doped contacts," *Nano Lett.*, vol. 5, no. 2, pp. 345–348, 2005.

- [18] G. S. Snider and P. J. Kuekes, "Nano state machines using hysteretic resistors and diode crossbars," *IEEE Trans. Nano.*, vol. 5, pp. 129–137, 2006.

- [19] W. Wang, T. Lee, and M. A. Reed, "Electrical characterization of self-assembled monolayers," in CRC Handbook on Molecular and Nano Electronics, S. E. Lyshevski, Ed. Boca Raton, FL: CRC, 2007.

- [20] R. Metzger, "Unimolecular electronics: Results and prospects," in CRC Handbook on Molecular and Nano Electronics, S. E. Lyshevski, Ed. Boca Raton, FL: CRC, 2007.

- [21] K. S. Kwok and J. C. Ellenbogen, "Moletronics: Future electronics," *Mater. Today*, vol. 5, no. 2, pp. 28–37, Feb. 1, 2002.

- [22] J. C. Ellenbogen and J. C. Love, "Architectures for molecular electronic computers. I. logic structures and an adder designed from molecular electronic diodes," *Proc. IEEE*, vol. 88, no. 3, pp. 386–426, Mar. 2000.

- [23] J. R. Heath, "Wires, switches, and wiring. A route toward a chemically assembled electronic nanocomputer," *Pure Appl. Chem.*, vol. 72, no. 1–2, pp. 11–20, 2000.

- [24] P. Beckett and A. Jennings, "Towards nanocomputer architecture," in Proc. Asia-Pacific Comp. Syst. Arch. Conf., 2002, pp. 141–150.

- [25] A. DeHon, "Array-based architecture for fet-based, nanoscale electronics," *IEEE Trans. Nanotechnol.*, vol. 2, no. 1, pp. 23–32, Mar. 2003.

- [26] A. DeHon, P. Lincoln, and J. E. Savage, "Stochastic assembly of sublithographic nanoscale interfaces," *IEEE Trans. Nanotechnol.*, vol. 2, no. 3, pp. 165–174, Sep. 2003.

- [27] A. DeHon and M. J. Wilson, "Nanowire-based sublithographic programmable logic arrays," in *Proc. ACM/SIGDA FPGA*, Monterey, CA, 2004, pp. 123–132.

- [28] M. Forshaw, R. Stadler, D. Crawley, and K. Nikolic, "A short review of nanoelectronic architectures," *Nanotechnology*, vol. 15, no. 4, pp. S220–S223, 2004.

- [29] J. R. Heath, P. J. Kuekes, G. S. Snider, and R. S. Williams, "A defect-tolerant computer architecture: Opportunities for nanotechnology," *Sci*, vol. 280, no. 5370, pp. 1716–1721, Jun. 12, 1998.

- [30] S. C. Goldstein and M. Budiu, "Nanofabrics: Spatial computing using molecular electronics," in *Proc. Int. Symp. Comp. Arch.*, Jun. 2001, pp. 178–191.

- [31] G. Snider, P. Kuekes, and R. S. Williams, "CMOS-like logic in defective, nanoscale crossbars," *Nanotechnology*, vol. 15, no. 8, pp. 881–891, Aug. 1, 2004.

- [32] G. S. Rose and M. R. Stan, "Memory arrays based on molecular RTD devices," in *Proc. IEEE-NANO*, 2003, pp. 453–456.

- [33] M. R. Stan, G. S. Rose, and M. M. Ziegler, "Hybrid cmos/molecular electronic circuits," in *Proc. 19th Int. Conf. VLSI Design Held Jointly* 5th Int. Conf. Embedded Syst. Design, Hyderabad, India, Jan. 2006, pp. 703–708.

- [34] Z. Zhong, D. Wang, Y. Cui, M. W. Bockrath, and C. M. Lieber, "Nanowire crossbar arrays as address decoders for integrated nanosystems," *Sci*, vol. 302, no. 5649, pp. 1377–1379, Nov. 21, 2003.

- [35] K. K. Likharev and D. B. Strukov, "CMOL: Devices, circuits, and architectures," *Lect. Notes Phys.*, vol. 680, pp. 447–478, 2005.

- [36] D. B. Strukov and K. K. Likharev, "Defect-tolerant architectures for nanoelectronic crossbar memories," *J. Nanosci. Nanotech.*, vol. 7, no. 1, pp. 151–167, Aug. 2006.

- [37] D. B. Strukov and K. K. Likharev, "A reconfigurable architecture for hybrid cmos/nanodevice circuits," in *Proc. ACM/SIGDA FPGA*, Monterey, CA, 2006.

- [38] W. Wu, G. Y. Jung, D. L. Olynick, J. Straznicky, Z. Li, X. Li, D. A. A. Ohlberg, Y. Chen, S. Y. Wang, J. A. Liddle, W. M. Tong, and R. S. Williams, "One-kilobit cross-bar molecular memory circuits at 30-nm half-pitch fabricated by nanoimprint lithography," *Appl. Phys.*, vol. 80, pp. 1173–1178, 2005.

- [39] P. J. Kuekes, G. S. Snider, and R. S. Williams, "Crossbar nanocomputers," Sci. Amer., pp. 72–80, Nov. 2005.

- [40] D. K. Brock, J. W. Ward, C. Bertin, B. M. Segal, and T. Rueckes, "Fabrication and applications of single-walled carbon nanotube fabrics," in *CRC Nanomanufacturing Handbook*, A. Busnaina, Ed. Boca Raton, FL: CRC, 2006, pp. 41–64.

- [41] J. E. Green, J. W. Choi, A. Boukai, Y. Bunimovich, E. Johnston-Halperin, E. DeIonno, Y. Luo, B. A. Sheriff, K. Xu, Y. S. Shin, H.-R. Tseng, J. F. Stoddart, and J. R. Heath, "A 160-kilobit molecular electronic memory patterned at 10<sup>11</sup> bits per square centimetre," *Nature*, vol. 445, pp. 414–417, 2007.

[42] G. S. Snider and R. S. Williams, "Nano/CMOS architectures using a

- [42] G. S. Snider and R. S. Williams, "Nano/CMOS architectures using a field-programmable nanowire interconnect," *Nanotechnology*, vol. 18, no. 035204, pp. 178–191, 2007.

- [43] K. S. J. Pister, J. M. Kahn, and B. E. Boser, "Smart dust: Wireless networks of millimeter-scale sensor nodes," in *Electron. Res. Lab. Res. Summary*, 1999.

- [44] R. A. Freitas, Jr., Nanomedicine. Austin, TX: Landes Bioscience, 1999, vol. I.

- [45] A. Cavalcanti and R. A. Freitas, Jr., "Nanorobotics control design: A collective behavior approach for medicine," *IEEE Trans. Nanobiosci.*, vol. 4, no. 2, pp. 133–140, Jun. 2005.

- [46] T. Hogg, "Coordinating microscopic robots for nanomedicine," presented at the 1st Very Small Robots Workshop, McLean, VA, Feb. 2005, unpublished.

- [47] SDR Forum, SDR Forum, Denver, CO [Online]. Available: http://www.sdrforum.org

- [48] M. Cummings and S. Haruyama, "FPGA in the software radio," *IEEE Commun. Mag.*, pp. 108–112, Feb. 1999.

- [49] RFID Journal, RFID Journal, Melville, NY [Online]. Available: http:// www.rfidjournal.com

- [50] D. Routenberg and J. C. Ellenbogen, Design for a millimeter-scale walking robot The MITRE Corporation, McLean, VA, report MP 0W00000010, 2000.

- [51] G. Snider, P. Kuekes, T. Hogg, and R. S. Williams, "Nanoelectronic architectures," Appl. Phys., vol. 80, no. 6, pp. 1183–1195, Mar. 2005.

- [52] S. R. Forrest and H. S. Hinton, Eds., *IEEE J. Quantum Elect., Spec. Iss. Smart Pixels*, vol. 29, no. 2, 1993.

- [53] R. M. Metzger, "All about (n-hexadecylquinolin-4-ium-1-yl) methylidenetricyanoquinodimethanide, a unimolecular rectifier of electrical current," J. Mater. Chem., vol. 10, pp. 55–62, 2000.

- [54] M. M. Ziegler, C. A. Picconatto, J. C. Ellenbogen, A. DeHon, D. Wang, Z. H. Zhong, and C. M. Lieber, "Scalability simulations for nanomemory systems integrated on the molecular scale," in *Molecular Electronics III*. New York: Ann. N.Y. Acad. Sci., 2003, vol. 1006, pp. 312–330.

- [55] R. M. Metzger, "Six unimolecular rectifiers and what lies ahead," *Lect. Notes Phys.*, vol. 680, pp. 313–350, 2005.

- [56] K. K. Likharev, "SET: Coulomb blockade devices," *Nano Et Micro Technol.*, vol. 3, pp. 71–114, 2003.

[57] Y. Cui and C. M. Lieber, "Functional nanoscale electronics devices

- [57] Y. Cui and C. M. Lieber, "Functional nanoscale electronics devices assembled using silicon nanowire building blocks," *Sci*, vol. 291, pp. 851–853, 2001.

- [58] D. R. Stewart, D. A. A. Ohlberg, P. A. Beck, Y. Chen, R. S. Williams, J. O. Jeppesen, K. A. Nielsen, and J. F. Stoddart, "Molecule-independent electrical switching in pt/organic monolayer/ti devices," *Nano Lett.*, vol. 4, no. 1, pp. 133–136, 2004.

- [59] S. Das, G. S. Rose, M. M. Ziegler, C. A. Picconatto, and J. C. Ellenbogen, "Architectures and simulations for nanoprocessor systems integrated on the molecular scale," *Lect. Notes Phys.*, vol. 680, pp. 479–512, 2005.

- [60] N. A. Melosh, A. Boukai, F. Diana, B. Gerardot, A. Badolato, P. M. Petroff, and J. R. Heath, "Ultrahigh-Density nanowire lattices and circuits," *Sci*, vol. 300, no. 5616, pp. 112–115, Apr. 4, 2003.

- [61] G. Y. Jung, S. Ganapathiappan, X. Li, D. A. A. Ohlberg, D. L. Olynick, Y. Chen, W. M. Tong, and R. S. Williams, "Fabrication of molecular-electronic circuits by nanoimprint lithography at low temperatures and pressures," *Appl. Phys. Mater. Sci. & amp; Process.*, vol. 78, no. 8, pp. 1169–1173, May 1, 2004.

- [62] G. Y. Jung, S. Ganapathiappan, D. A. A. Ohlberg, D. L. Olynick, Y. Chen, W. M. Tong, and R. S. Williams, "Fabrication of a 34 × 34 crossbar structure at 50-nm half-pitch by uv-based nanoimprint lithography," *Nano Lett.*, vol. 4, no. 7, pp. 1225–1229, 2004.

- [63] M. D. Austin, H. Ge, W. Wu, M. Li, Z. Yu, D. Wasserman, S. A. Lyon, and S. Y. Chou, "Fabrication of 5 nm linewidth and 14 nm pitch features by nanoimprint lithography," *Appl. Phys. Lett.*, vol. 84, no. 26, pp. 5299–5301, Jun. 2004.

- [64] D. Whang, S. Jin, Y. Wu, and C. M. Lieber, "Large-scale hierarchical organization of nanowire arrays for integrated nanosystems," *Nano Lett.*, vol. 3, no. 9, pp. 1255–1259, Sep. 2003.

- [65] S. Hollar, A. Flynn, C. Bellew, and K. S. J. Pister, "Solar powered 10 mg silicon robot," in *Proc. 16th Annu. Intl. IEEE Conf. MEMS*, 2003, pp. 706–711.

- [66] R. Yeh, S. Hollar, and K. S. J. Pister, "Design of low-power silicon articulated microrobots," *J. Micromechatronics*, vol. 1, no. 3, pp. 191–203, 2001.

- [67] M. Taczak, J. Ludwig, A. Gates, and J. C. Ellenbogen, "Millimeter-scale robotics at the MITRE corporation," presented at the 1st Very Small Robots Workshop, McLean, VA, Feb. 2005 [Online]. Available: http://www.mitre.org/tech/nanotech/ourwork/pdf/Millimeter-scale\_Robotics\_at\_MITRE.pdf, unpublished

- [68] R. D. Beer, R. D. Quinn, H. J. Chiel, and R. E. Ritzmann, "Biologically inspired approaches to robotics: What can we learn from insects?," *Commun. ACM*, vol. 40, no. 3, pp. 30–38, Mar. 1, 1997.

- [69] B. Lee and I. Lee, "The implementation of the gaits and body structure for hexapod robot," in *Proc. 2001 IEEE Intl. Symp. Indus. Elect.*, 2001, vol. 3, pp. 1959–1964.

- [70] D. B. Strukov and K. K. Likharev, "CMOL FPGA: A reconfigurable architecture for hybrid digital circuits with two-terminal nanodevices," *Nanotechnology*, vol. 16, pp. 888–900, 2005.

- [71] D. B. Strukov, "Digital architectures for hybrid cmos/nanodevice circuits," Ph.D. thesis, Stony Brook University, Stony Brook, NY, 2006.

[72] D. Hammerstrom, "Defect tolerant CMOL cell assignment via satisfia-

- [72] D. Hammerstrom, "Defect tolerant CMOL cell assignment via satisfiability," in Symp. Nanoelectronic Devices For Defense Security, Crystal City, VA, Jun. 2007.

- [73] X. M. H. Huang, C. A. Zorman, M. Mehregany, and M. L. Roukes, "Quality factor issues in silicon carbide nanomechnical resonators," in 12th Intl. Conf. Sol. St. Sens., Act. Microsys., 2003, pp. 722–725.

- [74] S. Das and M. F. Bauwens, "Clocking nanocircuits for nanocomputers and other nanoelectronic systems," in *Proc. IEEE/ACM Int. Symp. Nanoscale Architectures*, to be published.

- [75] M. R. Stan, P. D. Franzon, S. C. Goldstein, J. C. Lach, and M. M. Ziegler, "Molecular electronics: From devices and interconnect to circuits and architecture," *Proc. IEEE*, vol. 91, no. 11, pp. 1940–1957, Nov. 2003.

- [76] Cadence Design Framework II, Version IC 5.0.33, Cadence Design Systems, Inc., San Jose, CA, 2004.

- [77] TSMC Standard Cell Library Datasheet, Cadence Design Systems, Inc., San Jose, CA, Nov. 2006 [Online]. Available: http://www.ca-dence.com

- [78] Chip watch: Microprocessor Report, In-Stat, Waltham, MA, Sep. 2006 [Online]. Available: http://www.mdronline.com/mpr/chip\_watch/index.html

- [79] The Integrated Nanosystems Site, MITRE, McLean, VA, Sep. 2006 [Online]. Available: http://www.mitre.org/tech/nanotech/

- [80] LM741 Datasheet, Rev. 5.0, Fairchild Semiconductor, South Portland, ME, 2000 [Online]. Available: http://www.fairchildsemi.com

- [81] Intel Microprocessor Quick Reference Guide, Intel, Hillsboro, OR, Dec. 2006 [Online]. Available: http://www.intel.com/pressroom/kits/ quickreffam.htm

- [82] D. A. Johns and K. Martin, Analog Integrated Circuit Design. New York: Wiley, 1997.

- [83] L. Pan, M. Zhang, and Y. Nakayama, "Growth mechanism of carbon nanocoils," *J. Appl. Phys.*, vol. 91, no. 12, 2002.

- [84] P. C. P. Watts and W. K. Hsu, "Verification of electromagnetic induction from fe-filled carbon nanotubes," *Appl. Phys.*, vol. 78, pp. 79–83, 2004

- [85] D. C. Oertel, M. G. Bawendi, A. C. Arango, and V. Bulović, "Photode-tectors based on treated cdse quantum-dot films," *Appl. Phys. Lett.*, vol. 87, pp. 213 505-1–213 505-3, 2005.

- [86] M. S. Gudiksen, L. J. Lauhon, J. Wang, D. C. Smith, and C. M. Lieber, "Growth of nanowire superlattice structures for nanoscale photonics and electronics," *Nature*, vol. 415, pp. 617–620, 2002.

- [87] H. Kind, H. Yan, B. Messer, M. Law, and P. Yang, "Nanowire ultraviolet photodetectors and optical switches," Adv. Mat., vol. 14, no. 2, pp. 158–160, 2002.

- [88] F. Qian, Y. Li, S. Gradečak, D. Wang, C. J. Barrelet, and C. M. Lieber, "Gallium nitride-based nanowire radial heterostructures for nanophotonics," *Nano Lett.*, vol. 4, no. 10, pp. 1975–1979, 2004.

- [89] T. Kuykendall, P. J. Pauzauskie, Y. Zhang, J. Goldberger, D. Sirbuly, J. Denlinger, and P. Yang, "Crystallographic alignment of high-density galium nitride nanowire arrays," *Nature Mater.*, vol. 3, pp. 524–528, 2004.

- [90] R. Agarwal and C. M. Lieber, "Semiconductor nanowires: Optics and optoelectronics," *Appl. Phys.*, vol. 85, no. 3, pp. 209–215, 2006.

- [91] J. Timler and C. S. Lent, "Power gain and dissipation in quantum-dot cellular automata," J. Appl. Phys., vol. 91, no. 2, pp. 823–831, Jan. 15, 2002

- [92] C. S. Lent, B. Isaksen, and M. Lieberman, "Molecular quantum-dot cellular automata," *J. Amer. Chem. Soc.*, vol. 125, no. 4, pp. 1056–1063, 2003

- [93] Y. Huang, X. Duan, Q. Wei, and C. M. Lieber, "Directed assembly of one-dimensional nanostructures into functional networks," *Sci*, vol. 291, pp. 630–633, Jan. 2001.

- [94] R. T. Howe and C. G. Sodini, Microelectronics: An Integrated Approach. Upper Saddle River, NJ: Prentice-Hal, 1997.

- [95] M. A. Reed, "Quantum dots," Sci. Amer., pp. 118-123, Jan. 1993.

- [96] R. A. Pease, "What's all this transimpedance amplifier stuff, anyhow?," *Electron. Design*, Jan. 8, 2001.

- [97] I. O'Connor and F. Gaffiot, "Advanced research in on-chip optical interconnects," in *Low-Power Electronics Design*, C. Piguet, Ed. Boca Raton, FL: CRC, 2005.

- [98] P. Bai *et al.*, "A 65-nm logic technology featuring 35-nm gate lengths, enhanced channel strain, 8 cu interconnect layers, low-k ILD and 0.57- $\mu$ m<sup>2</sup> SRAM cell," in *Proc. IEDM*, Dec. 2004, pp. 657–660.

- [99] W.-H. Lee et al., "High-performance 65-nm SOI technology with enhanced transistor strain and advanced-low-k BEOL," in Proc. IEDM, Dec. 2005.

- [100] R. Turchetta, "Monolithic active pixel sensors: Design for science at CCLRC," in *PPARC Ind. Active Pixel Sensors Ind. Workshop*, London, U.K., Mar. 2004.

- [101] S. Mullen, "CMOS technology primer," Digital Content Producer Oct. 2006 [Online]. Available: http://www.digitalcontentproducer.com/hdhdv/depth/cmos\_tech\_hdv\_10092006/

**Shamik Das** (M'03) received the S.B. degree in mathematics, the S.B. and M.Eng. degrees in electrical engineering, and the Ph.D. degree in electrical engineering and computer science from the Massachusetts Institute of Technology (MIT), Cambridge, in 2000 and 2004, respectively.

He joined The MITRE Corporation, McLean, VA, in 2004. He leads the effort to design, simulate, and analyze nanoelectronic systems in the Nanosystems Group at MITRE. In that role, he has made important contributions to the development of prototypes

for extended nanomemory systems, as well as to the design and analysis of circuits for nanoprocessors. He has written and lectured broadly on the topic of nanoelectronic system design and simulation. In addition, he has been engaged in a number of other projects at MITRE, such as the design of novel techniques for hyperspectral imaging, analysis of bio-inspired electronics, and multi-scale modeling of physical systems. His technical interests include electronics above and beyond silicon, future computing systems, and systems engineering on the nanometer scale, as well as theoretical physics, acoustics, and pure mathematics.

In addition to the IEEE, Dr. Das is a member of Sigma Xi and Phi Beta Kappa.

**Alexander J. Gates** is presently working toward B.A. degrees in physics and mathematics at Cornell University, Ithaca, NY.

His research interests include nanoelectronic systems and materials. Since June 2004, Mr. Gates also has been employed as a Research Investigator in the Nanosystems Group, The MITRE Corporation, McLlean, VA, where he has worked on projects in nanoelectronic design and quantum molecular simulation.

**Hassen A. Abdu** (S'06) received the S.B. degree in electrical engineering from the Massachusetts Institute of Technology (MIT), Cambridge, in 2006. He currently is pursuing the M.Eng. degree in electrical engineering at MIT, where he is working on organic and quantum dot memory devices.

Since June 2004, Mr. Abdu also has been employed as a research investigator in the Nanosystems Group, The MITRE Corporation, McLean, VA, where he has worked on projects in nanoelectronic design and simulation.

Mr. Abdu is a member of Eta Kappa Nu and Sigma Xi.

Garrett S. Rose (S'98–M'06) received the B.S. degree in computer engineering from Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, in 2001 and the M.S. and Ph.D. degrees in electrical engineering from the University of Virginia, Charlottesville, in 2003 and 2006, respectively.

He is currently an Assistant Professor in the Department of Electrical and Computer Engineering at Polytechnic University, Brooklyn, NY. Since 2004, he also has worked part time with The MITRE Cor-

poration, McLean, VA, where he is involved in the simulation of nanoscale systems. His current research interests include VLSI circuit design and developing VLSI design methodologies for nanoelectronics, with a specific interest in molecular electronics.

Carl A. Picconatto received the B.S. degree in chemistry from the University of Notre Dame, Notre Dame, IN, and the Ph.D. degree in chemistry from Columbia University, New York, in 1993 and 2000, respectively.

He is the Lead Scientist in the Nanosystems Group, The MITRE Corporation, McLean, VA, and Principal Investigator of MITRE's Nano-Enabled Energy Storage Research Project. In addition, he serves as the nanotechnology laboratory director for the MITRE Biotechnology-Nanotechnology

Experimental Laboratory. His present research efforts include the use of nanotechnology for energy and power systems, materials research with carbon nanotubes, and theoretical investigations into the electrical characteristics of molecules. Previously, he led MITRE's effort to develop methods for the design and simulation of novel nanoelectronic memories and processors, which contributed greatly to the realization of the first prototype nanoelectronic systems.

Prior to joining MITRE, he served in the United States Congress as the Chief Science Advisor to Congresswoman Constance A. Morella, a senior member of the House Committee on Science. He also has worked for the Committee on Science, Engineering, and Public Policy at the National Academy of Sciences.

Dr. Picconatto is a member of the American Association for the Advancement of Science, American Chemical Society, and Phi Beta Kappa.

**James C. Ellenbogen** (M'03) received the B.A. degree in chemistry from the State University of New York, Buffalo, the M.S. degree in chemical physics from the University of Wisconsin, Madison, and the Ph.D. degree in chemical physics from the University of Georgia, Athens, in 1970, 1972 and 1977, respectively.

He is Senior Principal Scientist in the Nanosystems Group, The MITRE Corporation, McLean, VA, and Principal Investigator of MITRE's Nanosystems Modeling and Nanoelectronic Computers Research

Project. During the past 15 years, he has devoted his energies to furthering the science and technology for designing and developing nanosystems, such as electronic computers integrated on the nanometer scale. He has collaborated in the development of unique designs for molecular-scale electronic devices and co-authored several widely cited technical articles on nanoelectronics and nanotechnology. He has been instrumental in the realization of the first prototype nanoelectronic systems. His efforts in the design and simulation of nanoelectronic systems also have led to the discovery of new principles of physics that govern the electrical properties of molecular devices. He taught at several universities before joining The MITRE Corporation in 1984.

Dr. Ellenbogen is the recipient of the 1984 Barchi Prize of the Military Operations Research Society, the DARPA Ultra Electronics Program Outstanding Service Award in 1998, and the 2005 Washington Academy of Sciences Award for Work of Merit and Distinction in the Engineering Sciences.